|

|

|

https://gregdavill.github.io/OrangeCrab/ https://github.com/gregdavill/OrangeCrab [Mon Sep 14 13:46:12 2020] usb 2-2.3: new full-speed USB device number 8 using xhci_hcd [Mon Sep 14 13:46:12 2020] usb 2-2.3: New USB device found, idVendor=1209, idProduct=5af0, bcdDevice= 1.01 [Mon Sep 14 13:46:12 2020] usb 2-2.3: New USB device strings: Mfr=1, Product=2, SerialNumber=0 [Mon Sep 14 13:46:12 2020] usb 2-2.3: Product: OrangeCrab r0.2 DFU Bootloader v3.1 [Mon Sep 14 13:46:12 2020] usb 2-2.3: Manufacturer: GsD Microwatt with Linux on OrangeCrabhttps://codeconstruct.com.au/docs/microwatt-orangecrab/ ⦗OSS CAD Suite⦘ dpavlin@klin:/klin/FPGA/microwatt$ make microwatt.bit 2>&1 | tee ~/tmp/build1.txt

videogitdpavlin@klin:/klin/FPGA/CFU-Playground$ git remote -v origin https://github.com/google/CFU-Playground.git (fetch) origin https://github.com/google/CFU-Playground.git (push) dpavlin@klin:/klin/FPGA/CFU-Playground$ git submodule init dpavlin@klin:/klin/FPGA/CFU-Playground$ git submodule update ulx3s boardhttps://github.com/litex-hub/litex-boards/blob/master/litex_boards/targets/radiona_ulx3s.py dpavlin@klin:/klin/FPGA/CFU-Playground$ find . -name radiona_ulx3s.py ./third_party/python/litex_boards/litex_boards/targets/radiona_ulx3s.py ./third_party/python/litex_boards/litex_boards/platforms/radiona_ulx3s.py # edit fpga settings here dpavlin@klin:/klin/FPGA/CFU-Playground$ vi ./third_party/python/litex_boards/litex_boards/targets/radiona_ulx3s.py modifications for 85F litex-85f.diff buildyou really need riscv64 toolchain from https://github.com/sifive/freedom-tools/releases/tag/v2020.04.0-Toolchain.Only dpavlin@klin:/klin/FPGA/CFU-Playground/proj$ cat build.sh #!/bin/sh -xe echo https://github.com/google/CFU-Playground export PATH=/opt/riscv64-unknown-elf-gcc-8.3.0-2020.04.1-x86_64-linux-ubuntu14/bin/:$PATH export TARGET=radiona_ulx3s export UART_SPEED=115200 time make prog load sumulationdpavlin@klin:/klin/FPGA/CFU-Playground/proj/avg_pdti8$ time make PLATFORM=sim load -j 4 boot over serial using networkhost with ulx3s connectedroot@pihdmi:/home/pi# socat /dev/ttyUSB0,b115200,raw,echo=0 TCP:10.60.0.92:2003 machine running litexdpavlin@klin:/klin/FPGA/CFU-Playground/proj/hps_accel$ socat TCP-LISTEN:2003 PTY,link=ttyV2,raw

dpavlin@klin:/klin/FPGA/CFU-Playground/proj/hps_accel$ /klin/FPGA/CFU-Playground/soc/bin/litex_term --speed 115200 --serial-boot --kernel /klin/FPGA/CFU-Playground/proj/hps_accel/build/software.bin ttyV2 litex> serialboot Booting from serial... Press Q or ESC to abort boot completely. sL5DdSMmkekro [LXTERM] Received firmware download request from the device. [LXTERM] Uploading /klin/FPGA/CFU-Playground/proj/hps_accel/build/software.bin to 0x40000000 (1313688 bytes)... [LXTERM] Upload complete (9.9KB/s). [LXTERM] Booting the device. [LXTERM] Done. Executing booted program at 0x40000000 --============= Liftoff! ===============-- Hello, World! Board version: v7.0

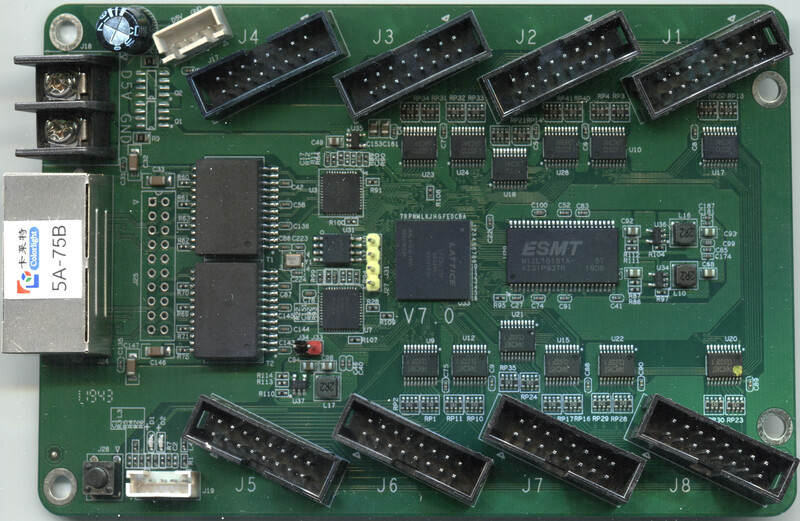

linkschubby75

original protocol

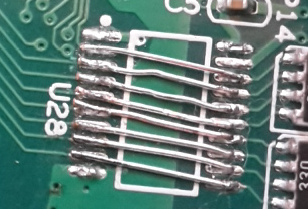

replace level shifters to get inputhttps://twitter.com/Claude1079/status/1231194849350647808

SN74CBT3245APW 8bit bidirectional FET switches  chiselwatthttps://github.com/antonblanchard/chiselwatt/commit/5a7fcbc8142ed2b390e1f8bfaaa801fe09a60351

UART RX is on J19, labelled key+ on the silk screen on the back LOCATE COMP "clock" SITE "P6";

LOCATE COMP "io_tx" SITE "F3"; litexbasic example of litex on colorLight 5A-75B based on fpga_101/lab004

fpga pin mappinghttps://twitter.com/adamgreig/status/1297255957320421383 I don't want to load a new image onto this totally blind, so I used the prjtrellis tools (https://github.com/YosysHQ/prjtrellis/) to write a script (https://github.com/adamgreig/cl/blob/master/pins.py) which works out input/output/bidi for all pins used in any ECP5 bitstream. It found only one unused pin... https://github.com/adamgreig/cl/blob/master/pins.py fpga images

List of useful (to me) FPGA resources: Books

Tools

Projects

X300 dongle

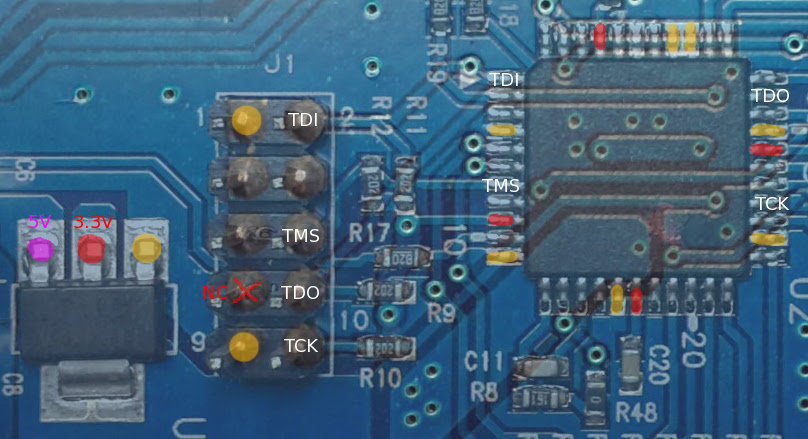

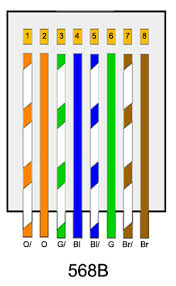

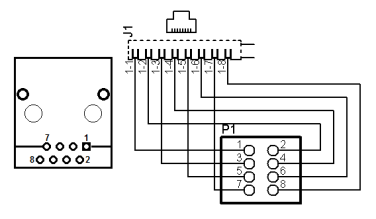

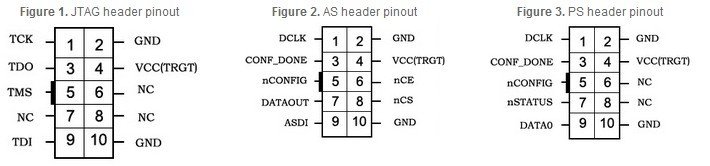

JTAGI took picture of both sides of board, corrected it using perspective tool in gimp and added layers with VCC (5V and 3.3V) and GND (checked with unimer continuity test).  JTAG pinout doesn't match silkscreen designation of pin 1 (it's rotated). It also doesn't have VCC pin connected, so you need to supply 5V power via other means (I used PS/2 connector). Bus Blaster jtag try: jtag> cable jtagkey vid=0x0403 pid=0x6010 interface=0 Connected to libftd2xx driver. jtag> detect IR length: 10 Chain length: 1 Device Id: 00010111000001100100000011011101 (0x170640DD) Manufacturer: Altera (0x0DD) Part(0): EPM3064A (0x7064) Stepping: 1 Filename: /usr/local/share/urjtag/altera/epm3064a/epm3064a jtag> print chain No. Manufacturer Part Stepping Instruction Register ------------------------------------------------------------------------------------------------------------------- * 0 Altera EPM3064A 1 BYPASS BYPASS # IMPORTANT: load signal aliases for this package jtag> include /usr/local/share/urjtag/altera/epm3064a/t44 # get values of all pins jtag> instruction SAMPLE/PRELOAD jtag> shift ir jtag> shift dr jtag> dr 010010111010111010010111010010010010111111111010111010 111010010010010111010010010010010010010010010010010010 010010010010010010010010010010010010010010010010010010 010010010010010111010111010010 (0x0000000000000000000000000000000024924924924975D2) jtag> print chain No. Manufacturer Part Stepping Instruction Register ------------------------------------------------------------------------------------------------------------------- * 0 Altera EPM3064A 1 SAMPLE/PRELOAD BSR jtag> get signal IO2 IO2 = 1 jtag> get signal IO3 IO3 = 1 jtag> get signal IO43 IO43 = 1 jtag> get signal IO44 IO44 = 1 # toggle single pin jtag> instruction EXTEST jtag> shift ir jtag> print chain No. Manufacturer Part Stepping Instruction Register ------------------------------------------------------------------------------------------------------------------- * 0 Altera EPM3064A 1 EXTEST BSR jtag> set signal IO10 out 0 jtag> shift dr # re-read values of all pins jtag> instruction SAMPLE/PRELOAD jtag> shift ir jtag> shift dr jtag> get signal IO10 IO10 = 0 SVF programmingjtag> svf /blue-zfs/FPGA/Altera-x300/x300_dongle/output_files/dongle1.svf stop progress detail: Parsing 20/520 ( 3%)warning: unimplemented mode 'ABSENT' for TRST detail: Parsing 520/520 (100%)detail: detail: Scanned device output matched expected TDO values. VHDL to toggle pinsToggle pins on all four sides of CPLD and create additional two images with all one and all zero for easy test where pin is dongle1.vhdThen I connected logic analyzer on pins and tried different svf files (all-0, all-1, left, bottom, right, top) to locate which pin change depending on image loaded. To isolate pins I used EXTEST and toggled pins. RJ45

PS2http://www.computer-engineering.org/ps2protocol/

6-pin Mini-DIN (PS/2): Keyboard (left, purple)

Mouse (right, green)

Audio jackR2R D2A all measurements are done on Hantek 2090 with 500mV/div setting which may account for some accuracy errors channel 1

channel 2

Bunch of references for Altera FPGA JTAG pinout Bus Pirate programmingThe Bus Pirate can program CPLDs and FPGAs using XSVF format bitstreams and XSVF player firmware. Altera might not output XSVF directly, but there is a simple converter for SVF to XSVF.

Windows binaries are provided, but the source should also compile under Linux. Source is in the Bus Pirate SVN:

Bus Pirate FPGA and CPLD programming with XSVF:

SVF to XSVF converter: USB BlasterFX2LP firmware

QuartusCreate SVF filehttp://www.altera.com/support/kdb/solutions/rd07222008_677.html To generate an SVF file in Quartus® II software, follow the steps below:

manual pin assigmentedit .*qsf file and add: set_location_assignment PIN_AP30 -to qdr_q[35] 13.0sp1 startdpavlin@klin:~$ /opt/altera/13.0sp1/quartus/bin/quartus --64bit Altera hardware

ReferencesRaspberryPiFPGA

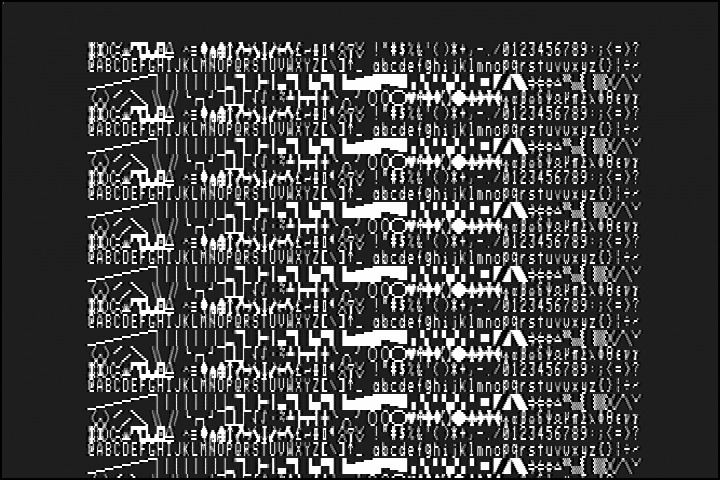

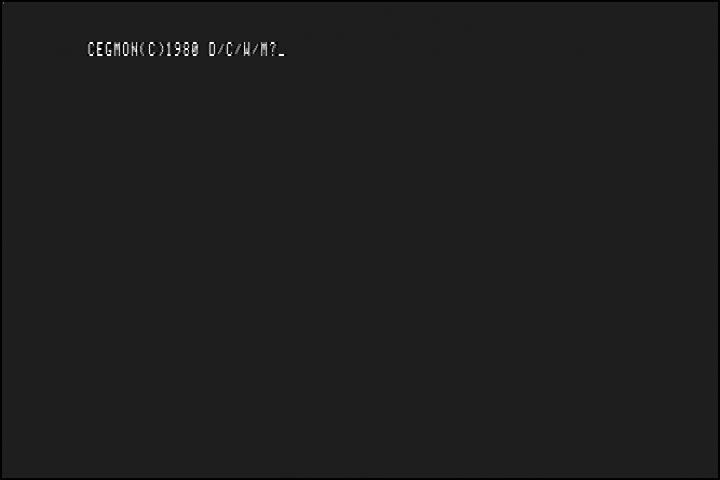

Stereo vision  dpavlin@blue:/bluez/FPGA/ULX2S/uk101$ KERNEL[16887.354856] add /devices/pci0000:00/0000:00:1a.0/usb3/3-1/3-1.1/3-1.1.3 (usb) KERNEL[16887.358543] add /devices/pci0000:00/0000:00:1a.0/usb3/3-1/3-1.1/3-1.1.3/3-1.1.3:1.0 (usb) UDEV [16887.365476] add /devices/pci0000:00/0000:00:1a.0/usb3/3-1/3-1.1/3-1.1.3 (usb) KERNEL[16888.370326] add /module/usbserial (module) KERNEL[16888.370344] add /bus/usb-serial (bus) KERNEL[16888.370378] add /bus/usb/drivers/usbserial (drivers) KERNEL[16888.370396] add /bus/usb/drivers/usbserial_generic (drivers) KERNEL[16888.370413] add /bus/usb-serial/drivers/generic (drivers) UDEV [16888.370685] add /module/usbserial (module) UDEV [16888.370725] add /bus/usb-serial (bus) UDEV [16888.370879] add /bus/usb/drivers/usbserial (drivers) UDEV [16888.370901] add /bus/usb-serial/drivers/generic (drivers) UDEV [16888.370928] add /bus/usb/drivers/usbserial_generic (drivers) KERNEL[16888.371900] add /module/ftdi_sio (module) KERNEL[16888.371923] add /bus/usb/drivers/ftdi_sio (drivers) KERNEL[16888.371945] add /bus/usb-serial/drivers/ftdi_sio (drivers) UDEV [16888.371980] add /module/ftdi_sio (module) UDEV [16888.372050] add /bus/usb-serial/drivers/ftdi_sio (drivers) KERNEL[16888.372098] add /devices/pci0000:00/0000:00:1a.0/usb3/3-1/3-1.1/3-1.1.3/3-1.1.3:1.0/ttyUSB0 (usb-serial) UDEV [16888.372124] add /bus/usb/drivers/ftdi_sio (drivers) KERNEL[16888.372401] add /devices/pci0000:00/0000:00:1a.0/usb3/3-1/3-1.1/3-1.1.3/3-1.1.3:1.0/ttyUSB0/tty/ttyUSB0 (tty) UDEV [16888.372546] add /devices/pci0000:00/0000:00:1a.0/usb3/3-1/3-1.1/3-1.1.3/3-1.1.3:1.0 (usb) UDEV [16888.372888] add /devices/pci0000:00/0000:00:1a.0/usb3/3-1/3-1.1/3-1.1.3/3-1.1.3:1.0/ttyUSB0 (usb-serial) UDEV [16888.374650] add /devices/pci0000:00/0000:00:1a.0/usb3/3-1/3-1.1/3-1.1.3/3-1.1.3:1.0/ttyUSB0/tty/ttyUSB0 (tty) KERNEL[16929.333395] add /devices/pci0000:00/0000:00:1a.0/usb3/3-1/3-1.6/3-1.6.3 (usb) KERNEL[16929.333629] add /devices/pci0000:00/0000:00:1a.0/usb3/3-1/3-1.6/3-1.6.3/3-1.6.3:1.0 (usb) UDEV [16929.338304] add /devices/pci0000:00/0000:00:1a.0/usb3/3-1/3-1.6/3-1.6.3 (usb) UDEV [16929.338759] add /devices/pci0000:00/0000:00:1a.0/usb3/3-1/3-1.6/3-1.6.3/3-1.6.3:1.0 (usb) KERNEL[16929.708966] add /devices/pci0000:00/0000:00:1a.0/usb3/3-1/3-1.6/3-1.6.3/3-1.6.3.2 (usb) KERNEL[16929.712382] add /devices/pci0000:00/0000:00:1a.0/usb3/3-1/3-1.6/3-1.6.3/3-1.6.3.2/3-1.6.3.2:1.0 (usb) KERNEL[16929.712433] add /devices/pci0000:00/0000:00:1a.0/usb3/3-1/3-1.6/3-1.6.3/3-1.6.3.2/3-1.6.3.2:1.0/media0 (media) KERNEL[16929.773679] add /devices/pci0000:00/0000:00:1a.0/usb3/3-1/3-1.6/3-1.6.3/3-1.6.3.2/3-1.6.3.2:1.0/video4linux/video0 (video4linux) KERNEL[16929.773733] add /devices/pci0000:00/0000:00:1a.0/usb3/3-1/3-1.6/3-1.6.3/3-1.6.3.2/3-1.6.3.2:1.0/input/input30 (input) KERNEL[16929.773790] add /devices/pci0000:00/0000:00:1a.0/usb3/3-1/3-1.6/3-1.6.3/3-1.6.3.2/3-1.6.3.2:1.0/input/input30/event16 (input) KERNEL[16929.773883] add /devices/pci0000:00/0000:00:1a.0/usb3/3-1/3-1.6/3-1.6.3/3-1.6.3.2/3-1.6.3.2:1.1 (usb) KERNEL[16929.942458] add /devices/pci0000:00/0000:00:1a.0/usb3/3-1/3-1.6/3-1.6.3/3-1.6.3.3 (usb) KERNEL[16929.943007] add /devices/pci0000:00/0000:00:1a.0/usb3/3-1/3-1.6/3-1.6.3/3-1.6.3.3/3-1.6.3.3:1.0 (usb) KERNEL[16929.943064] add /devices/pci0000:00/0000:00:1a.0/usb3/3-1/3-1.6/3-1.6.3/3-1.6.3.3/3-1.6.3.3:1.0/video4linux/video2 (video4linux) UDEV [16929.949326] add /devices/pci0000:00/0000:00:1a.0/usb3/3-1/3-1.6/3-1.6.3/3-1.6.3.2 (usb) UDEV [16929.949933] add /devices/pci0000:00/0000:00:1a.0/usb3/3-1/3-1.6/3-1.6.3/3-1.6.3.2/3-1.6.3.2:1.1 (usb) UDEV [16929.949946] add /devices/pci0000:00/0000:00:1a.0/usb3/3-1/3-1.6/3-1.6.3/3-1.6.3.2/3-1.6.3.2:1.0 (usb) UDEV [16929.950176] add /devices/pci0000:00/0000:00:1a.0/usb3/3-1/3-1.6/3-1.6.3/3-1.6.3.3 (usb) UDEV [16929.950550] add /devices/pci0000:00/0000:00:1a.0/usb3/3-1/3-1.6/3-1.6.3/3-1.6.3.2/3-1.6.3.2:1.0/media0 (media) UDEV [16929.950861] add /devices/pci0000:00/0000:00:1a.0/usb3/3-1/3-1.6/3-1.6.3/3-1.6.3.2/3-1.6.3.2:1.0/input/input30 (input) UDEV [16929.951576] add /devices/pci0000:00/0000:00:1a.0/usb3/3-1/3-1.6/3-1.6.3/3-1.6.3.2/3-1.6.3.2:1.0/input/input30/event16 (input) UDEV [16929.952469] add /devices/pci0000:00/0000:00:1a.0/usb3/3-1/3-1.6/3-1.6.3/3-1.6.3.2/3-1.6.3.2:1.0/video4linux/video0 (video4linux) UDEV [16930.953075] add /devices/pci0000:00/0000:00:1a.0/usb3/3-1/3-1.6/3-1.6.3/3-1.6.3.3/3-1.6.3.3:1.0 (usb) UDEV [16930.954337] add /devices/pci0000:00/0000:00:1a.0/usb3/3-1/3-1.6/3-1.6.3/3-1.6.3.3/3-1.6.3.3:1.0/video4linux/video2 (video4linux) dpavlin@blue:/bluez/FPGA/ULX2S/uk101$ dpavlin@blue:/bluez/FPGA/ULX2S/uk101$ ../ujprog-x86-64 ./uk101-ulx2s8k.jed ULX2S JTAG programmer v 1.07 $Id: ujprog.c 1748 2014-01-09 15:07:43Z marko $ KERNEL[17115.768270] remove /devices/pci0000:00/0000:00:1a.0/usb3/3-1/3-1.1/3-1.1.3/3-1.1.3:1.0/ttyUSB0/tty/ttyUSB0 (tty) KERNEL[17115.768305] remove /devices/pci0000:00/0000:00:1a.0/usb3/3-1/3-1.1/3-1.1.3/3-1.1.3:1.0/ttyUSB0 (usb-serial) Using USB JTAG cable. UDEV [17115.769313] remove /devices/pci0000:00/0000:00:1a.0/usb3/3-1/3-1.1/3-1.1.3/3-1.1.3:1.0/ttyUSB0/tty/ttyUSB0 (tty) UDEV [17115.769664] remove /devices/pci0000:00/0000:00:1a.0/usb3/3-1/3-1.1/3-1.1.3/3-1.1.3:1.0/ttyUSB0 (usb-serial) Programming: 100% Completed in 5.88 seconds. dpavlin@blue:/bluez/FPGA/ULX2S/uk101$ loaderhttps://github.com/GadgetFactory/Papilio-Loader/pull/6 dpavlin@blue:/blue-zfs/FPGA/Papilio$ git clone https://github.com/GadgetFactory/Papilio-Loader.git dpavlin@blue:/blue-zfs/FPGA/Papilio$ cd Papilio-Loader/papilio-prog dpavlin@blue:/blue-zfs/FPGA/Papilio/Papilio-Loader/papilio-prog$ git checkout -b revert-libftdi2 261d0dd02f5489c63e8227c6f916af5efacfbe7a dpavlin@blue:/blue-zfs/FPGA/Papilio/Papilio-Loader/papilio-prog$ ./autogen.sh dpavlin@blue:/blue-zfs/FPGA/Papilio/Papilio-Loader/papilio-prog$ ./configure && make # check compiled binary dpavlin@blue:/blue-zfs/FPGA/Papilio/Papilio-Loader/papilio-prog$ ./papilio-prog -v -j Using built-in device list JTAG chainpos: 0 Device IDCODE = 0x24001093 Desc: XC6SLX9 USB transactions: Write 3 read 2 retries 1 ZAP IDEcompilationdpavlin@blue:/blue-zfs/FPGA/Papilio$ git clone https://github.com/GadgetFactory/ZAP--ZPUino-Arduino-Papilio--IDE.git dpavlin@blue:/blue-zfs/FPGA/Papilio$ cd ZAP--ZPUino-Arduino-Papilio--IDE/build/ dpavlin@blue:/blue-zfs/FPGA/Papilio/ZAP--ZPUino-Arduino-Papilio--IDE/build$ ant dpavlin@blue:/blue-zfs/FPGA/Papilio/ZAP--ZPUino-Arduino-Papilio--IDE/build/linux$ ln -s zpu_tools_linux32.tar.bz2 zpu_tools_linux64.tar.bz2 fix papilio-prog to use Linux binary

dpavlin@blue:/blue-zfs/FPGA/Papilio/ZAP--ZPUino-Arduino-Papilio--IDE/build/linux/work$ vi ./hardware/zpuino/zpu/platform.txt

# fix papilioprog to papilio-prog

tools.papilioprog.cmd=papilio-prog

# remove .exe from this line

tools.papilioprog.erase.pattern="{path}/bin/papilio-prog" -c

dpavlin@blue:/blue-zfs/FPGA/Papilio/ZAP--ZPUino-Arduino-Papilio--IDE/build/linux/work$ chmod 755 hardware/tools/papilio/papilio_loader/Papilio_Programmer.sh

# copy compiled papilio-prog to correct location and fix permissions

dpavlin@blue:/blue-zfs/FPGA/Papilio/ZAP--ZPUino-Arduino-Papilio--IDE/build/linux/work$ cp ../../../../Papilio-Loader/papilio-prog/papilio-prog hardware/tools/papilio/papilio_loader/bin/

dpavlin@blue:/blue-zfs/FPGA/Papilio/ZAP--ZPUino-Arduino-Papilio--IDE/build/linux/work$ chmod 755 hardware/tools/papilio/papilio_loader/bin/papilio-prog

running IDERun arduino GUI: dpavlin@blue:/blue-zfs/FPGA/Papilio/ZAP--ZPUino-Arduino-Papilio--IDE/build/linux/work$ ./arduino Compilation works, but programming doesn't with error: Board: Unknown board @ 96000000 Hz (0xa4041700) so, let's rebuild zpuprogrammer dpavlin@blue:/blue-zfs/ZPUino/ZPUino-HDL/zpu/hdl/zpuino/programmer$ git remote -v origin https://github.com/alvieboy/ZPUino-HDL/ (fetch) origin https://github.com/alvieboy/ZPUino-HDL/ (push) dpavlin@blue:/blue-zfs/ZPUino/ZPUino-HDL/zpu/hdl/zpuino/programmer$ autoreconf --install dpavlin@blue:/blue-zfs/ZPUino/ZPUino-HDL/zpu/hdl/zpuino/programmer$ ./configure dpavlin@blue:/blue-zfs/ZPUino/ZPUino-HDL/zpu/hdl/zpuino/programmer$ make dpavlin@blue:/blue-zfs/ZPUino/ZPUino-HDL/zpu/hdl/zpuino/programmer$ cp zpuinoprogrammer /blue-zfs/FPGA/Papilio/ZAP--ZPUino-Arduino-Papilio--IDE/build/linux/dist/tools/ # this one is for already built version dpavlin@blue:/blue-zfs/ZPUino/ZPUino-HDL/zpu/hdl/zpuino/programmer$ cp zpuinoprogrammer /blue-zfs/FPGA/Papilio/ZAP--ZPUino-Arduino-Papilio--IDE/build/linux/work/hardware/tools/zpu/bin/zpuinoprogrammer program boot file (IDE doesn't have permission to do so) dpavlin@blue:/blue-zfs/FPGA/Papilio$ ./papilio-prog -v -f ./zap-2.0.5/hardware/zpuino/zpu/bootloaders/lx9/zpuino-1.0-PapilioPro-S6LX9-RetroCade-1.0.bit Using built-in device list JTAG chainpos: 0 Device IDCODE = 0x24001093 Desc: XC6SLX9 Created from NCD file: papilio_pro_routed.ncd;UserID=0xFFFFFFFF Target device: 6slx9tqg144 Created: 2012/11/20 00:16:43 Bitstream length: 2727072 bits Uploading "./zap-2.0.5/hardware/zpuino/zpu/bootloaders/lx9/zpuino-1.0-PapilioPro-S6LX9-RetroCade-1.0.bit". DNA is 0x190efd25eb57c9fe Done. Programming time 549.2 ms USB transactions: Write 176 read 8 retries 5 run IDE dpavlin@blue:/blue-zfs/FPGA/Papilio/ZAP--ZPUino-Arduino-Papilio--IDE/build/linux/work$ ./arduino Experimental: JNI_OnLoad called. Stable Library ========================================= Native lib Version = RXTX-2.1-7 Java lib Version = RXTX-2.1-7 verification will fail, so just upload sketch: dpavlin@blue:/blue-zfs/FPGA/Papilio/Papilio-SOC/zpu/hdl/zpuino/programmer$ ./zpuinoprogrammer -s 1000000 -R -d /dev/ttyUSB1 -b /tmp/build383944339812357036.tmp/Autoscroll.cpp.bin -U Board: GadgetFactory Papilio Pro LX9 @ 96000000 Hz (0xa4041700) Upload completed successfully in 0.05 seconds. zpugccdpavlin@blue:/blue-zfs/FPGA/Papilio$ git clone git://repo.or.cz/zpugcc.git Cloning into 'zpugcc'... remote: Counting objects: 35519, done. remote: Compressing objects: 100% (26110/26110), done. remote: Total 35519 (delta 8445), reused 35519 (delta 8445) Receiving objects: 100% (35519/35519), 70.18 MiB | 426.00 KiB/s, done. Resolving deltas: 100% (8445/8445), done. Checking connectivity... done. Checking out files: 100% (35311/35311), done. dpavlin@blue:/blue-zfs/FPGA/Papilio$ cd zpugcc/toolchain dpavlin@blue:/blue-zfs/FPGA/Papilio/zpugcc/toolchain$ git diff build.sh diff --git a/toolchain/build.sh b/toolchain/build.sh index 783beaa..034929c 100644 --- a/toolchain/build.sh +++ b/toolchain/build.sh @@ -3,6 +3,9 @@ set -e rm -rf build mkdir build cd build +mkdir bin +ln -s /bin/true bin/makeinfo +export PATH=`pwd`/bin:$PATH ../binutils/configure --target=zpu-elf --prefix=`pwd`/../install make make install dpavlin@blue:/blue-zfs/FPGA/Papilio/zpugcc/toolchain$ sh -x build.sh RetroCade MegaWinghttp://retrocade.gadgetfactory.net/index.php?n=Main.RetroCadeMegaWing LCDModify Examples/LiqueidCrystal/Autoscroll

// initialize the library with the numbers of the interface pins

LiquidCrystal lcd(26, 24, 23, 22, 21, 20);

void setup() {

// contrast to GND

pinMode(46, OUTPUT);

digitalWrite(46, LOW);

// RW to ground

pinMode(25, OUTPUT);

digitalWrite(25, LOW);

// set up the LCD's number of columns and rows:

lcd.begin(16,2);

}

ZPU (without Arduino IDE)Xilinx Virtual Cable DaemonCheap(er) China Proxmark

Mifare sniff/crackhttp://code.google.com/p/crapto1/

http://www.youtube.com/watch?v=kTvb7tjbSTI Proxmark firmware comparison on emulated Mifare 4k

Usage

proxmark3> hw version

#db# Prox/RFID mark3 RFID instrument

#db# bootrom: svn 816 2013-10-11 22:09:42

#db# os: svn 816 2013-10-11 22:09:43

#db# FPGA image built on 2012/ 1/ 6 at 15:27:56

uC: AT91SAM7S256 Rev B

Embedded Processor: ARM7TDMI

Nonvolatile Program Memory Size: 256K bytes

Second Nonvolatile Program Memory Size: None

Internal SRAM Size: 64K bytes

Architecture Identifier: AT91SAM7Sxx Series

Nonvolatile Program Memory Type: Embedded Flash Memory

proxmark3> hw tune

#db# Measuring antenna characteristics, please wait...

#db# Measuring complete, sending report back to host

# LF antenna: 0.00 V @ 125.00 kHz

# LF antenna: 0.00 V @ 134.00 kHz

# LF optimal: 0.00 V @ 12000.00 kHz

# HF antenna: 7.28 V @ 13.56 MHz

# Your LF antenna is unusable.

proxmark3> hf 14a read

ATQA : 02 00

UID : ?? ?? ?? ??

SAK : 38 [1]

TYPE : Nokia 6212 or 6131 MIFARE CLASSIC 4K

ATS : 0d 78 f7 b1 02 4a 43 4f 50 76 32 34 31 27 cc

- TL : length is 13 bytes

- T0 : TA1 is present, TB1 is present, TC1 is present, FSCI is 8

- TA1 : different divisors are NOT supported, DR: [2, 4, 8], DS: [2, 4, 8]

- TB1 : SFGI = 0, FWI = 8

- TC1 : NAD is NOT supported, CID is supported

- HB : 4a 43 4f 50 76 32 34 31

brute force 26-bit proxcardfirmware version

According to http://wiki.radiowar.org/Proxmark3%E5%9B%BA%E4%BB%B6%E5%88%97%E8%A1%A8 Google translated version Please do not upgrade your firmware to the CDC Proxmark3 version r617 ~ r830 driver's! We found that because the problem will lead to Proxmark3 code appears unable to identify high-frequency card, and 816 will appear after Nested number of keys for 000000000000. flashing updatedpavlin@blue:/blue-zfs/FPGA/proxmark/proxmark3$ make flash-all Compile new version of firmwareAll instructions below this are for old version of software see http://www.proxmark.org/forum/viewtopic.php?id=1668 http://code.google.com/p/proxmark3/wiki/Compiling je strgan http://www.proxmark.org/forum/post/3244/#p3244 sudo apt-get install build-essential libreadline5 libreadline-dev libusb-0.1-4 libusb-dev libqt4-dev perl pkg-config dpavlin@t61p:/tank/proxmark3$ svn co http://proxmark3.googlecode.com/svn/trunk proxmark3 Boot loader

dpavlin@t61p:/tank/proxmark3/proxmark3$ ./client/flasher -b ./bootrom/obj/bootrom.elf

Loading ELF file './bootrom/obj/bootrom.elf'...

Loading usable ELF segments:

0: V 0x00100000 P 0x00100000 (0x00000200->0x00000200) [R X] @0x94

1: V 0x00200000 P 0x00100200 (0x000017a8->0x000017a8) [R X] @0x294

Waiting for Proxmark to appear on USB...

Connected units:

1. SN: ? [004/013]

Found.

Entering bootloader...

(Press and release the button only to abort)

Waiting for Proxmark to reappear on USB....

Connected units:

1. SN: ? [004/014]

Found.

Flashing...

Writing segments for file: ./bootrom/obj/bootrom.elf

0x00100000..0x001001ff [0x200 / 2 blocks].. OK

0x00100200..0x001019a7 [0x17a8 / 24 blocks]........................ OK

Resetting hardware...

All done.

Have a nice day!

^

dpavlin@t61p:/tank/proxmark3/proxmark3$ ./client/flasher ./armsrc/obj/fullimage.elf

Loading ELF file './armsrc/obj/fullimage.elf'...

Loading usable ELF segments:

0: V 0x00102000 P 0x00102000 (0x0000a4bc->0x0000a4bc) [R ] @0xb4

1: V 0x00110000 P 0x00110000 (0x0000ba8c->0x0000ba8c) [R X] @0xa570

2: V 0x00200000 P 0x0011ba8c (0x00000004->0x00000004) [RW ] @0x15ffc

Note: Extending previous segment from 0xba8c to 0xba90 bytes

Waiting for Proxmark to appear on USB...

Connected units:

1. SN: ? [004/015]

Found.

Entering bootloader...

(Press and release the button only to abort)

Waiting for Proxmark to reappear on USB....

Connected units:

1. SN: ChangeMe [004/016]

Found.

Flashing...

Writing segments for file: ./armsrc/obj/fullimage.elf

0x00102000..0x0010c4bb [0xa4bc / 165 blocks]..................................................................................................................................................................... OK

0x00110000..0x0011ba8f [0xba90 / 187 blocks]........................................................................................................................................................................................... OK

Resetting hardware...

All done.

Have a nice day!

|

Weblog Archives

|