Dobrica Pavlinušić's random unstructured stuff

hi3515v100: Revision 7

hi3515v100.pdf

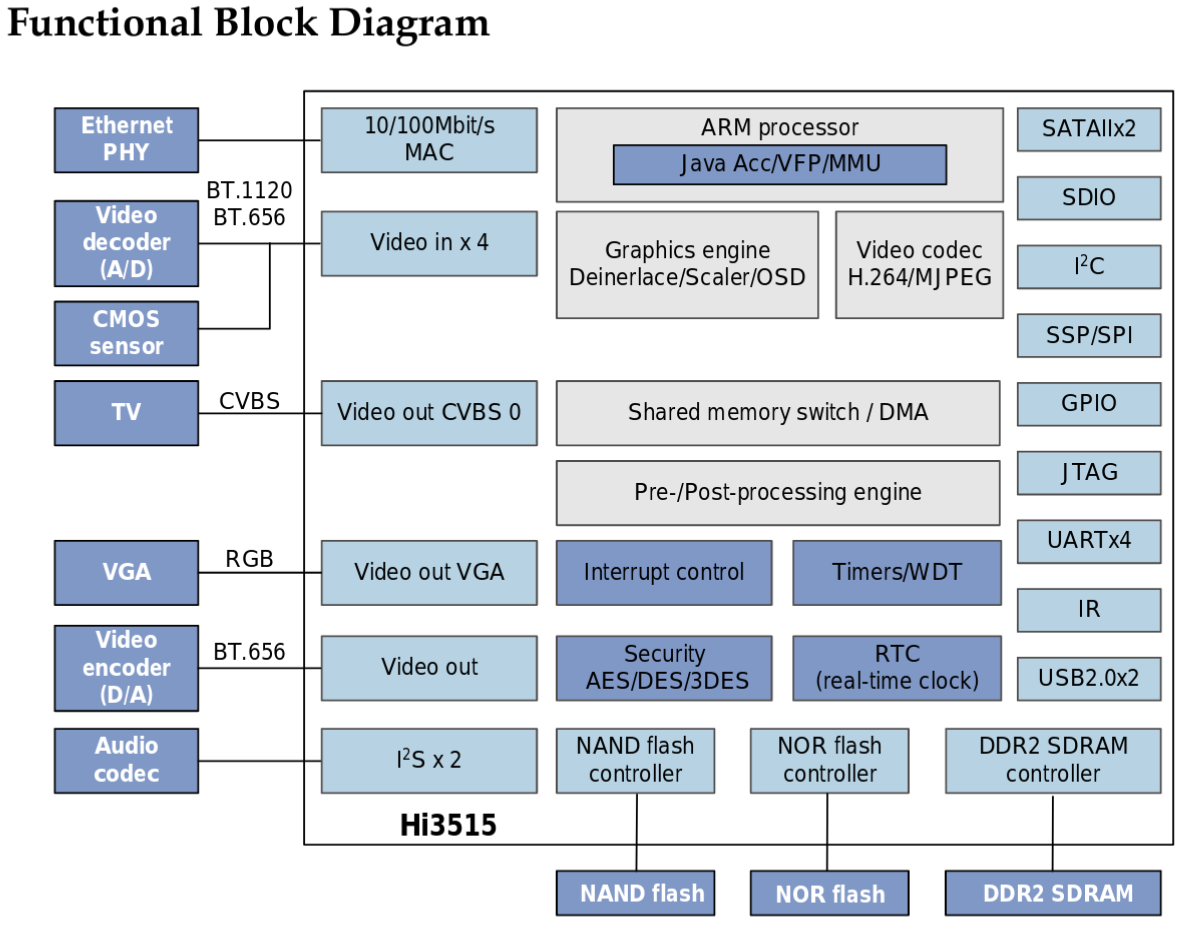

Hi3515Hi3515 H.264 Encoding and Decoding Processor

Key Features

CPU Core

zARM926EJ

I-cache 16 KB, D-cache 16 KB

I-TCM 2 KB

Built-in MMU, supporting multiple open operating systems such as VxWorks, Linux, WinCE, and PalmOS

Up to 400 MHz operating frequency

Video Encoding/Decodingz

H.264 main profile encoding/decoding

H.264 baseline profile encoding/decoding

JPEG/MJPEG baseline encoding/decoding

serial

EN-6704V 4 channel H.264 digital video recorder for @RadionaOrg has 3.3V uart with pinout GND, TX, RX, 5V

hi3515v100

links

http://www.i-1.nl/blog/wp-content/uploads/CCF-paper-Forensic-reliabilty-DVR.pdf